# Simplification of Boolean functions

Using the theorems of Boolean Algebra, the algebraic forms of functions can often be simplified, which leads to simpler (and cheaper) implementations.

## Example 1

$$F = A.B + A.B + B.C$$

= A. (B + B) + B.C

= A.1 + B.C

= A + B.C

How many gates do you save from this simplification?

#### Example 2

$$F = \overline{A.B.C} + \overline{A.B.C} + \overline{A.B.C} + \overline{A.B.C}$$

$$= \overline{A.B.C} + \overline{A.B.C} + \overline{A.B.C} + \overline{A.B.C} + \overline{A.B.C} + \overline{A.B.C}$$

$$= (\overline{A.B.C} + \overline{A.B.C}) + (\overline{A.B.C} + \overline{A.B.C}) + (\overline{A.B.C} + \overline{A.B.C})$$

$$= (\overline{A} + \overline{A}). B.C + (\overline{B} + B). C.A + (\overline{C} + C). A.B$$

$$= B.C + C.A + A.B$$

- Example 3 Show that A + A.B = A

- A + AB

- = A.1 + A.B

- = A. (1 + B)

- = A.1

- = A

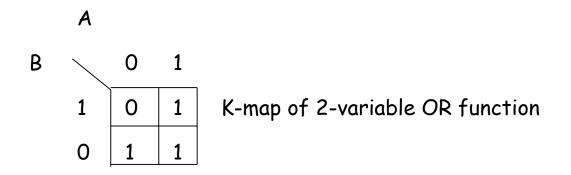

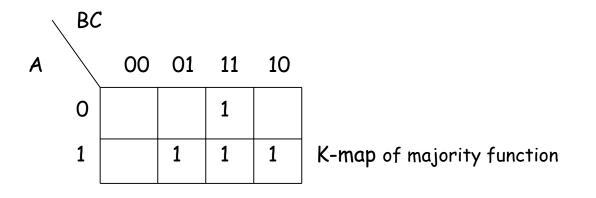

## Simplification using Karnaugh Maps

Follow the class lectures to understand how to simplify Boolean functions using K-maps. Several examples will be worked out in the class.

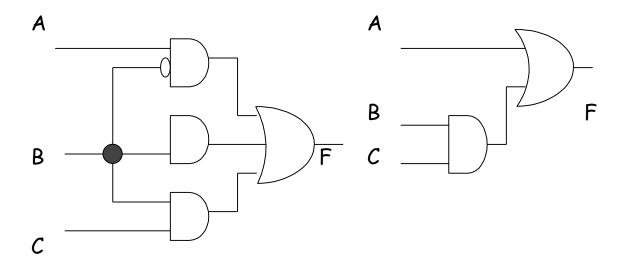

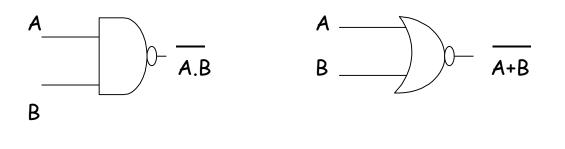

## Other types of gates

NAND gate

NOR gate

Be familiar with the truth tables of these gates.

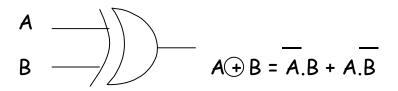

Exclusive OR (XOR) gate

#### NAND and NOR are universal gates

Any function can be implemented using only NAND or only NOR gates. How can we prove this?

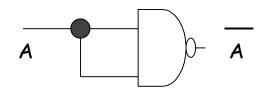

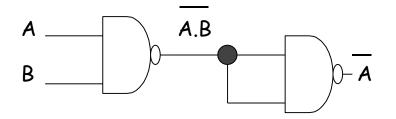

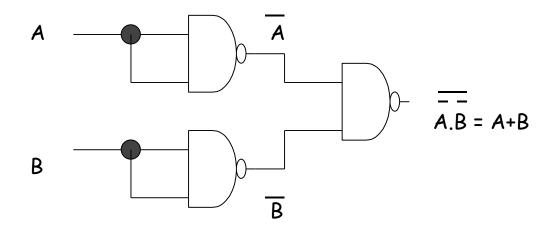

(Proof for NAND gates) Any boolean function can be implemented using AND, OR and NOT gates. So if AND, OR and NOT gates can be implemented using NAND gates only, then we prove our point.

1. Implement NOT using NAND

#### 2. Implementation of AND using NAND

#### 1. Implementation of OR using NAND

(Exercise) Prove that NOR is a universal gate.

#### Example (to be worked out in class)

How to convert any circuit that uses AND, OR and NOT gates to a version that uses NAND (or NOR gates only)?

#### Additional properties of XOR

XOR is also called modulo-2 addition. Why?

| Α | В | С | F |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

|   |   |   |   |

$A \oplus B = 1$  only when there are an odd number of 1's in (A,B). The same is true for  $A \oplus B \oplus C$  also.

$$\begin{array}{c}

1 \oplus A = \overline{A} \\

0 \oplus A = A

\end{array}$$

Why?

## Logic Design Exercise

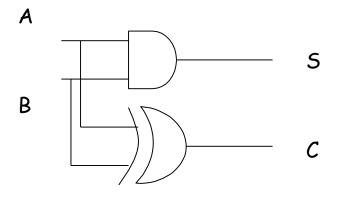

## <u>Half Adder</u>

$$A \longrightarrow Half Sum (S)$$

$$A \longrightarrow Adder Garry (C)$$

$$S = A \oplus B$$

$$C = A.B$$

| A | В | 5 | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

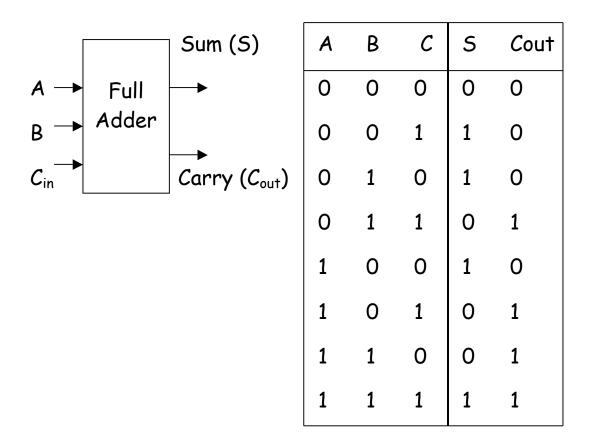

#### Full Adder

$S = A \oplus B \oplus C_{in}$  $C_{out} = A.B + B.C_{in} + A.C_{in}$

How can you add two 32-bit numbers? It will be discussed in the class.

## <u>Combinational vs. Sequential Circuits</u>

#### Combinational circuits.

The output depends only on the current values of the inputs and not on the past values. Examples are adders, subtractors, and all the circuits that we have studied so far

#### Sequential circuits.

The output depends not only on the current values of the inputs, but also on their past values. These hold the secret of how to memorize information. We will study sequential circuits later.

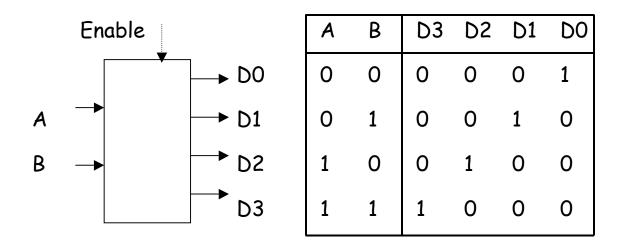

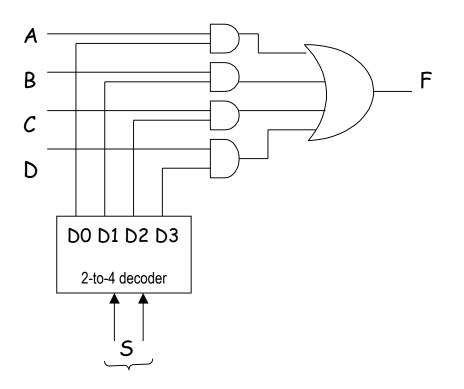

## <u>Decoders</u>

A typical decoder has n inputs and 2<sup>n</sup> outputs.

A 2-to-4 decoder and its truth table.

| D3 = A.B              |  |

|-----------------------|--|

| D2 = A.B              |  |

| D1 = A.B              |  |

| $DO = \overline{A.B}$ |  |

|                       |  |

Draw the circuit of this decoder. The decoder works per specs when (Enable = 1). When Enable = 0, all the outputs are 0.

**Exercise**. Design a 3-to-8 decoder.

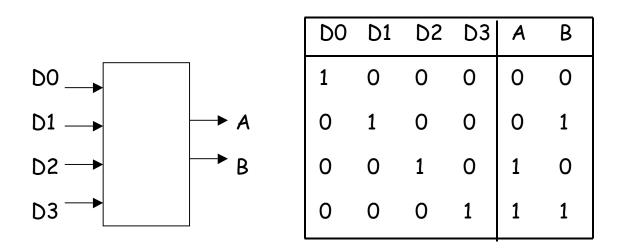

## <u>Encoders</u>

A typical encoder has 2<sup>n</sup> inputs and n outputs.

A 4-to-2 encoder and its truth table.

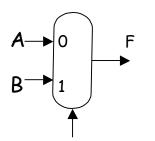

## <u>Multiplexor</u>

It is a many-to-one switch, also called a selector.

S = 0, F = A S = 1, F = B

Control S

Specifications of the mux

A 2-to-1 mux

$F = \overline{S}$ . A + S. B

Exercise. Design a 4-to-1 mux.

#### Another design of a decoder

Exercise 1. Design a 2-to-4 decoder using 1-to-2 decoders only.

Exercise 2. Design a 4-to-1 multiplexor using 2-1 multiplexors only.

To be discussed in the class.

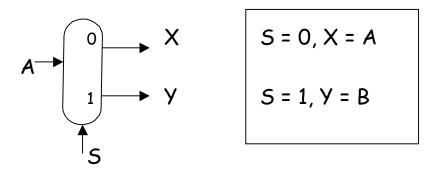

#### Demultiplexors

A demux is a one-to-many switch.

A 1-to-2 demux, and its specification.

So, X = S. A, and Y = S. B

**Exercise**. Design a 1-4 demux.

We will discuss the design of a 1-bit ALU in class.